Parity is a fundamental technique used in error detection within digital communication systems. It involves adding an extra bit, known as the parity bit, to a string of binary data to ensure that the total count of 1s is either even or odd. This method helps identify single-bit errors that may occur during data transmission by checking if the parity condition is met upon reception. In the context of technology, even parity and odd parity are the two main types of parity used for error detection. For instance, in even parity, the parity bit is set so that the total number of 1s in the data plus the parity bit is even. This approach is widely implemented in memory systems and communication protocols to maintain data integrity by detecting errors early in the process.

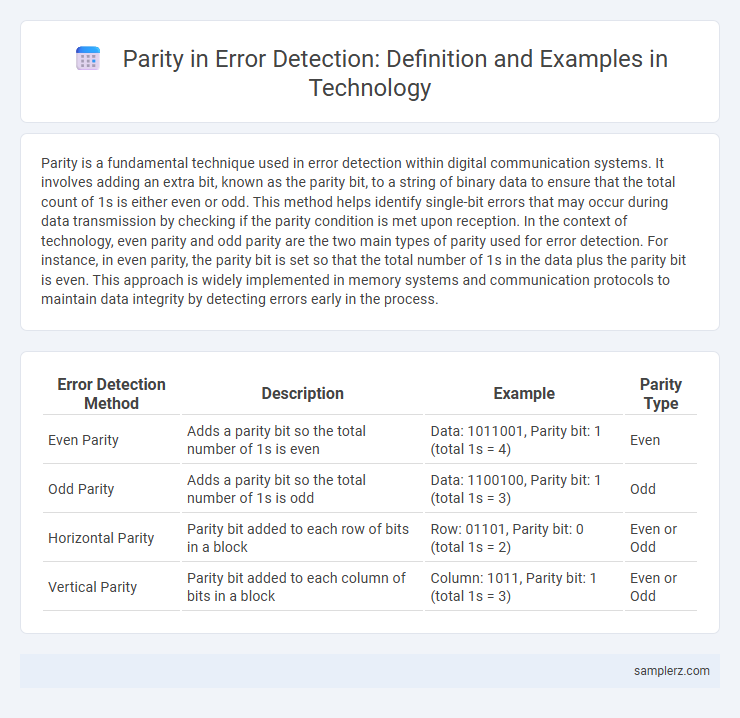

Table of Comparison

| Error Detection Method | Description | Example | Parity Type |

|---|---|---|---|

| Even Parity | Adds a parity bit so the total number of 1s is even | Data: 1011001, Parity bit: 1 (total 1s = 4) | Even |

| Odd Parity | Adds a parity bit so the total number of 1s is odd | Data: 1100100, Parity bit: 1 (total 1s = 3) | Odd |

| Horizontal Parity | Parity bit added to each row of bits in a block | Row: 01101, Parity bit: 0 (total 1s = 2) | Even or Odd |

| Vertical Parity | Parity bit added to each column of bits in a block | Column: 1011, Parity bit: 1 (total 1s = 3) | Even or Odd |

Introduction to Parity in Error Detection

Parity in error detection employs a simple binary scheme where a single parity bit is added to data bits to ensure the total number of ones is either even (even parity) or odd (odd parity). This method detects single-bit errors by checking parity consistency during data transmission, making it a fundamental error-checking technique in digital communication systems. Parity bits are widely used in memory systems, communication protocols, and data storage devices to maintain data integrity with minimal overhead.

The Concept of Parity Bits Explained

Parity bits serve as a fundamental error detection mechanism by appending an extra bit to data to ensure the total number of 1s is either even or odd, depending on the parity scheme. In an even parity system, the parity bit is set to 1 if the count of 1s in the data is odd, making the overall count even for error checking. This simple technique helps identify single-bit errors during data transmission in communication protocols and memory storage devices.

Even Parity Example in Data Communication

Even parity in data communication ensures error detection by appending a parity bit to a binary data set, making the total number of 1s even. For instance, the 7-bit data 1011001 contains four 1s, so the parity bit is set to 0 to maintain even parity. During transmission, the receiver checks the parity bit and data bits; a mismatch indicates an error, prompting retransmission or correction protocols.

Odd Parity Example for Data Integrity

Odd parity error detection ensures data integrity by adding a parity bit to each data byte, making the total number of 1s in the byte odd. For example, if the 7-bit data is 1011001 (which has four 1s), the parity bit is set to 1 to create 10110011, resulting in five 1s. During transmission, if the parity of received data does not remain odd, an error is detected, prompting retransmission to maintain data accuracy.

Parity Check in Memory Modules

Parity check in memory modules is a fundamental error detection technique that ensures data integrity by verifying whether the number of set bits is even or odd. Each memory word is appended with a parity bit, which is set to maintain either even parity or odd parity, allowing the system to detect single-bit errors during read operations. This method is widely used in RAM modules and cache memory to prevent data corruption and improve system reliability.

Real-World Applications of Parity Error Detection

Parity error detection is widely used in memory systems such as dynamic RAM and cache memory to ensure data integrity by identifying single-bit errors during data storage or retrieval. Storage devices like hard drives and solid-state drives implement parity checks to detect errors in data blocks, improving reliability in data transfer and storage processes. Network communication protocols, including Ethernet and serial communication interfaces, utilize parity bits to detect transmission errors, enabling error correction mechanisms for more robust data exchange.

Parity Implementation in Network Protocols

Parity implementation in network protocols utilizes parity bits to detect errors during data transmission by appending an extra bit that indicates whether the number of set bits is odd or even. Common protocols such as asynchronous serial communication and early Ethernet standards employ even or odd parity schemes to identify single-bit errors within each transmitted byte or frame. This simple yet effective error detection technique enhances data integrity by enabling immediate error recognition without requiring complex algorithms or additional bandwidth.

Advantages and Limitations of Parity Error Detection

Parity error detection offers a simple and cost-effective method for identifying single-bit errors in data transmission by appending a parity bit for even or odd parity schemes. The key advantage is its low overhead and ease of implementation in hardware, making it suitable for real-time applications with minimal resource consumption. However, parity checking cannot detect multiple-bit errors or correct any errors, limiting its effectiveness in environments with higher error rates or complex data integrity requirements.

Parity-Based Error Detection vs. ECC

Parity-based error detection uses a single parity bit to identify single-bit errors by ensuring the total number of 1s is even or odd, making it simple but limited in detecting multiple errors. Error-Correcting Code (ECC) memory employs advanced algorithms like Hamming code to both detect and correct multi-bit errors, significantly enhancing data reliability in critical systems. ECC is prevalent in servers and high-performance computers, while parity-based detection remains common in simpler or cost-sensitive applications.

Future Trends in Parity Error Detection Technologies

Future trends in parity error detection technologies emphasize the integration of machine learning algorithms to enhance real-time error prediction and correction accuracy. Advancements in quantum computing are driving the development of parity schemes capable of handling complex data structures and high-dimensional error patterns. Emerging IoT networks demand lightweight parity protocols optimized for low power consumption and scalable error detection across distributed devices.

example of parity in error detection Infographic

samplerz.com

samplerz.com